### **Machine Learning in Computational Lithography**

Yu Cao

**ASML-Brion**

San Jose, February 2019

#### **ASML**

Public Slide 2

#### What's Happening and What's the Meaning:

G Dan Hutcheson

**ASML introduces Al to its product portfolio:** This is really a no-brainer. That said, the problem that most equipment companies have is finding good applications for it, as they find all they have is little data to feed the NN (more on that below). Anyway, this will be a good test for DLNNs as to whether engineers will accept results without knowing what's in the 'blackbox,' which is a classic barrier to this technology. I believe they will because comparing results to input consistency are pretty easy to test out in this case. Especially since ASML led the way into computational lithography, albeit with plenty of customer pull.

Source: The Chip Insider® VLSIresearch

## Machine learning brings revolution to many applications! **ASML**

Public Slide 3

#### Can machine learning be the moonshot for us?

ecurity & Counterterrorism: Fighting Security & Counterterrorism: Chasing

Security & Counterterrorism: Chasin

Mining: Production Safety

Banking: ATM Protection

Intruder Alerts

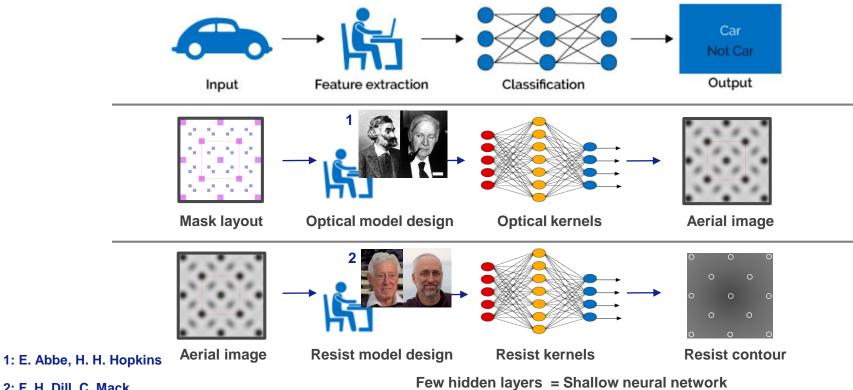

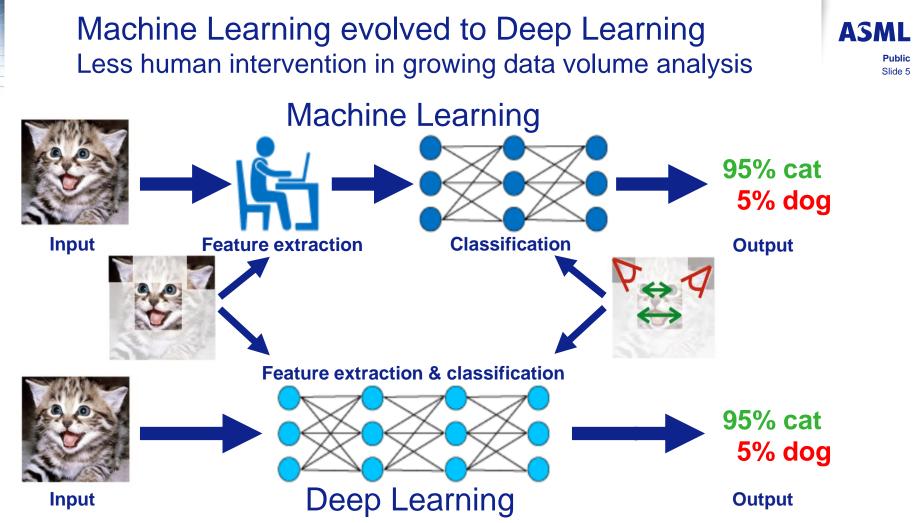

We have been doing machine learning for a long time .... ASML Public with manual feature engineering Slide 4

Machine Learning

2: F. H. Dill, C. Mack

Public

Based on: Jagreet Kaur Gill, "Log Analytics With Deep Learning And Machine Learning" April 28, 2017

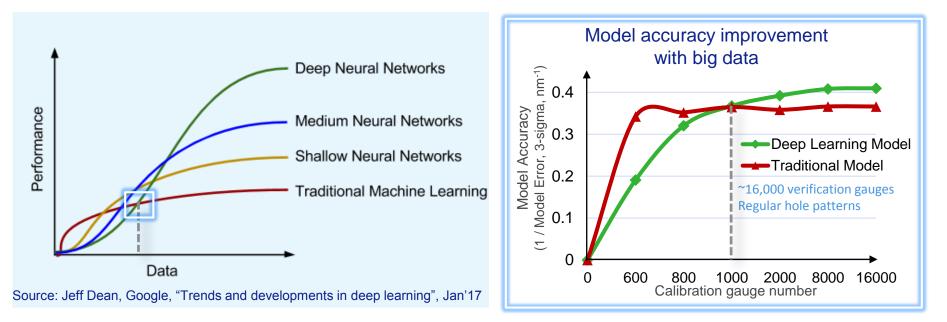

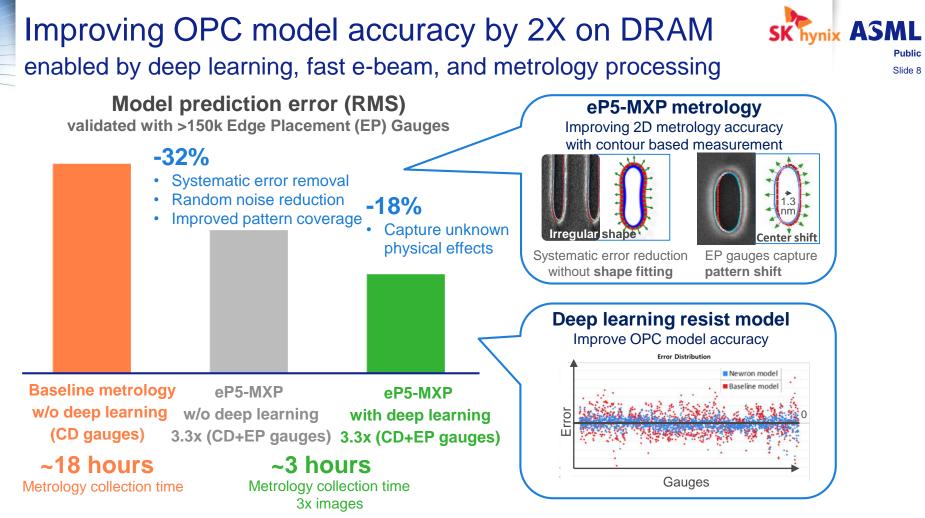

# Massive metrology data & deep learning models further improve OPC accuracy in customer case

ASML Public Slide 6

- Big data improve pattern coverage & enhance model accuracy

- Deep Learning Model has more benefits with big data vs Traditional Model

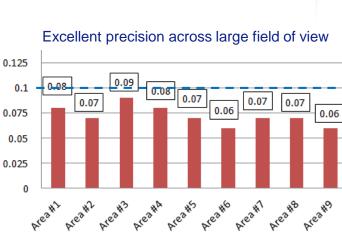

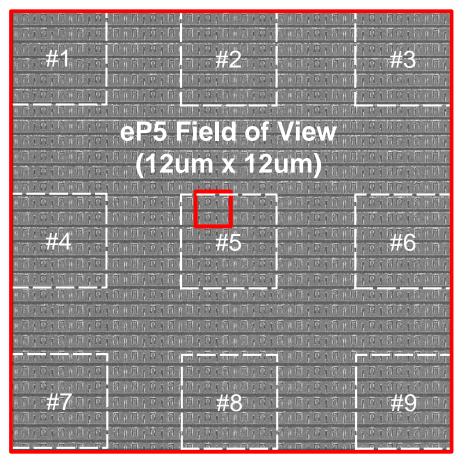

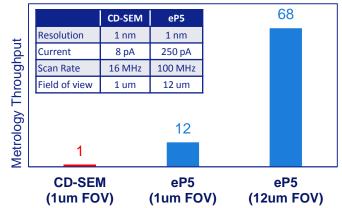

### High speed e-beam metrology and large field of view

CD repro (nm)

ASML

OPC Model accuracy study using high volume contour based gauges and deep learning on memory device, Young-Seok Kim et al., SPIE 2019, 10959-37

#### Better accuracy of lithography models by deep learning ASML Enabled by fast e-beam metrology and physical based models Public Slide 9 Model Prediction Accuracy (RMS in nm) Physical driven training using physics based lithography models EUV Cases: 7 nm and 5 nm logic Stability 1.0 **ASML** Deep 0.7 0.5 0.4 Learning model 0.34 0.32 **Physical** Resist Data expansion 1D 2D 1D 2DResist surface through simulated Shrinkage contours stress DUV Cases: 7 nm and 5 nm logic Data-driven training based on fitting 1.0 0.8 spec and wafer measurements 0.4 **Accuracy EP SET1** EP SET2 1D 2D 0000000000 00000000000 with Deep Learning 00000000000 without Deep Learning Large volume wafer metrology data, further enhanced by fast e-beam "EP SET1" → Edge Placement Gauge Set 1

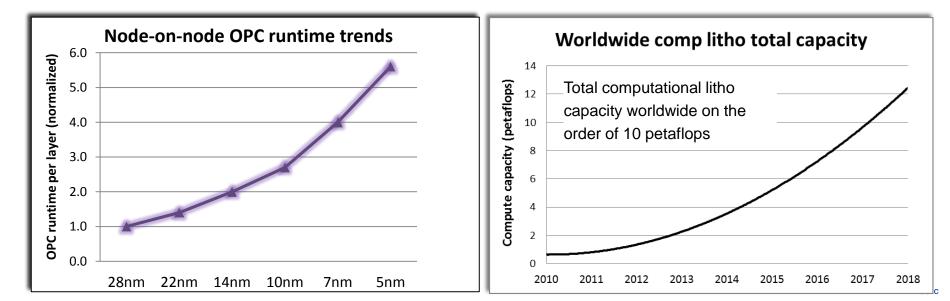

#### "Moore's Law" of Computational Lithography Runtime and cost of OPC increases node-by-node

Public Slide 10

| Technology Node                                       | 28nm | 22nm | 14nm | 10nm | 7nm  | 5nm   |

|-------------------------------------------------------|------|------|------|------|------|-------|

| Production start                                      | 2011 | 2013 | 2014 | 2016 | 2017 | 2019  |

| Average transistor density (billion/cm <sup>2</sup> ) | 1.17 | 1.63 | 2.34 | 3.75 | 6.25 | 10.71 |

| Number of critical layer masks                        | 18   | 24   | 33   | 37   | 47   | 66    |

| Normalized OPC runtime per layer per unit area        | 1    | 1.4  | 2    | 2.7  | 4    | 5.6   |

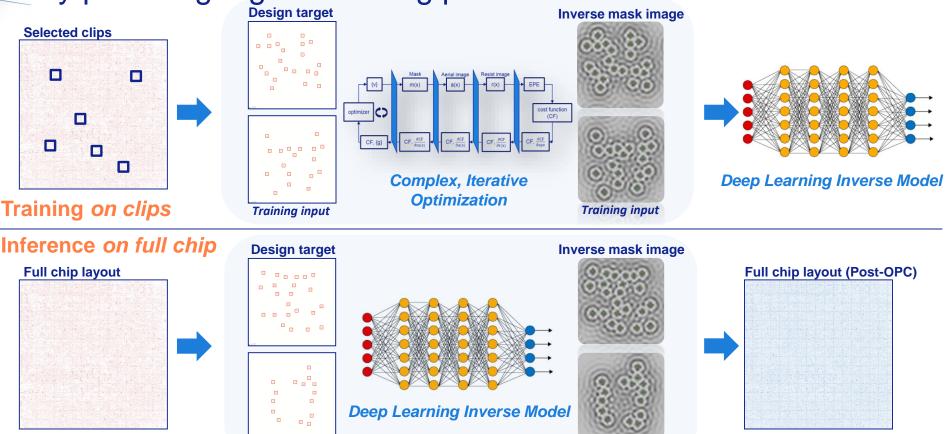

# Deep learning inverse model speeds up full-chip OPC by providing a good starting point

ASML

Public Slide 11

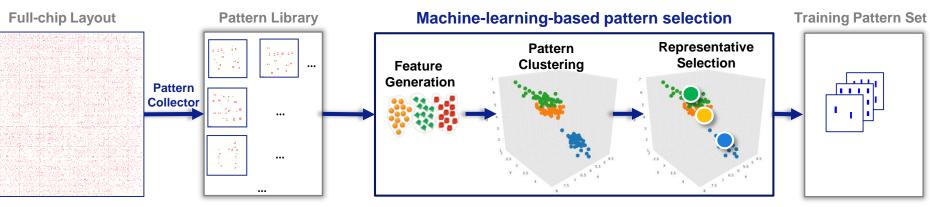

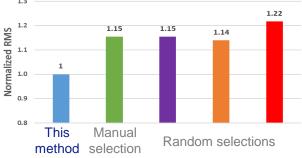

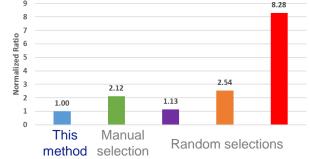

## Improving training pattern coverage using machine-learning-based pattern selection

Public Slide 12

Normalized RMS between prediction and ground-truth (inverse solution)

Critical PV-band (>15% CD error ) Comparison

Full-chip application of machine learning SRAFs on DRAM case using auto pattern selection K. Chen et al., SPIE 2019, 10961-37

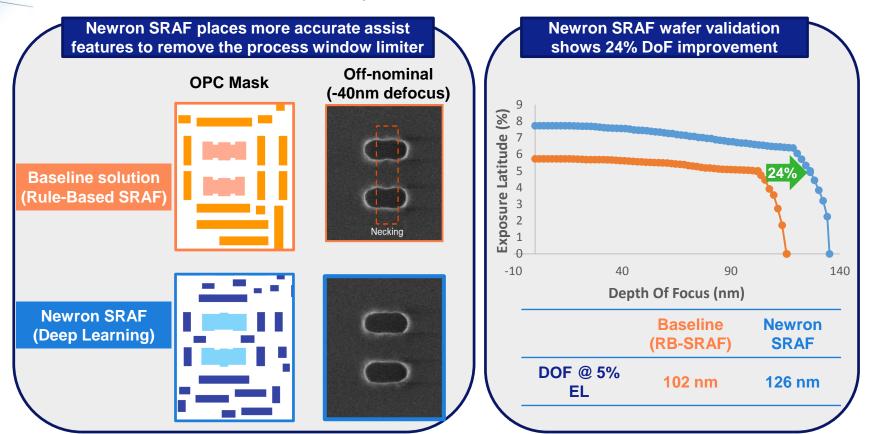

# Deep learning SRAF improves full-chip DoF by 24% for DRAM contact hole layer, validated on wafer

Slide 13

Full-chip application of machine learning SRAFs on DRAM case using auto pattern selection K. Chen et al., SPIE 2019, 10961-37

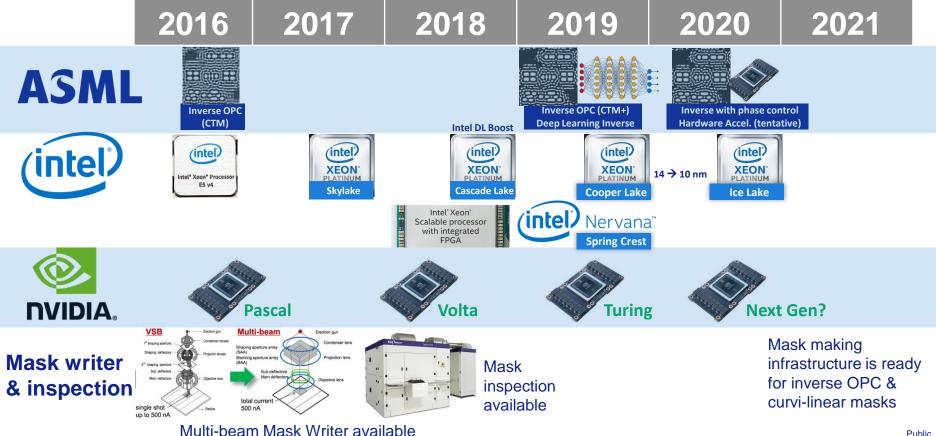

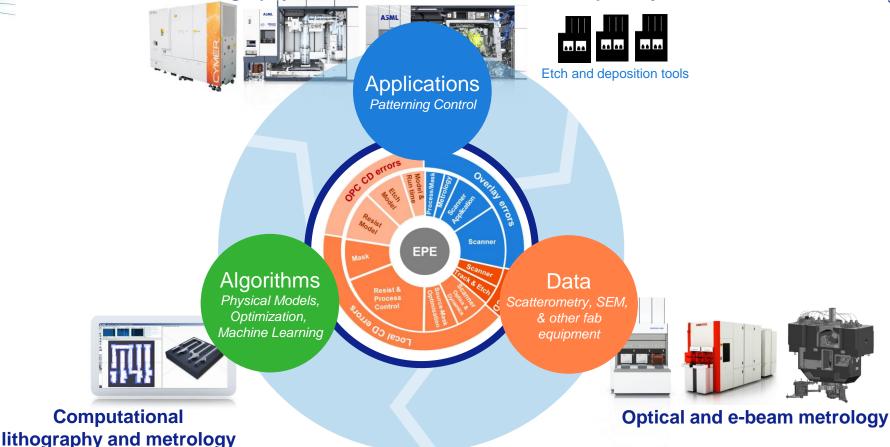

#### Leverage confluence of new technologies to meet OPC ASML technology and cost requirements

Public

Public

Slide 14

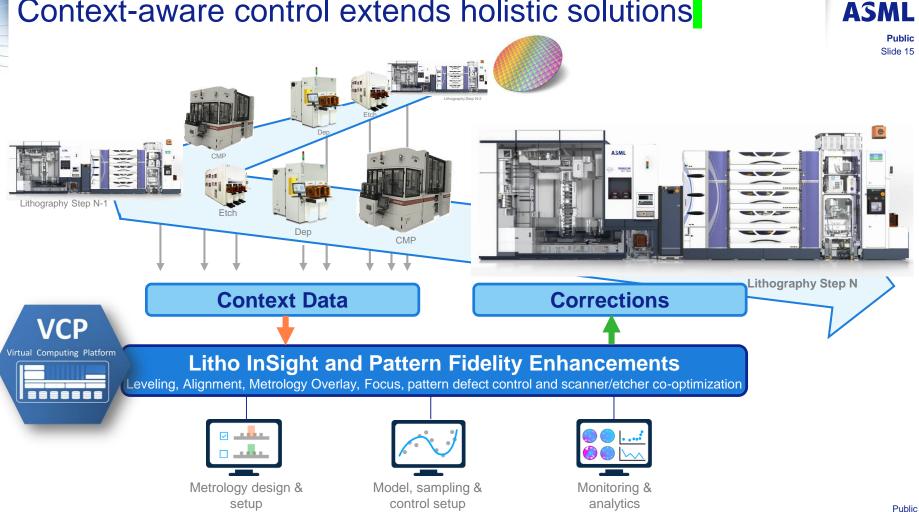

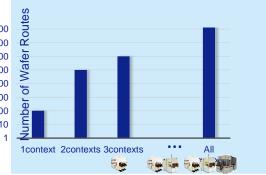

### Context-aware control extends holistic solutions

# Leverage machine learning to address wafer-to-wafer variation induced by different wafer process routes

ASML

Public Slide 16

#### **Overlay Variations**

Different Process Route

Wafer to Wafer Variation

ASML Machine Learning Model

Correlate wafer-to-wafer variation to process context and apply runto-run control with context-based grouping

A novel patterning control strategy based on real-time fingerprint recognition and adaptive wafer level scanner optimization H. E. Hakli et al., SPIE 2018, 10585:105851N

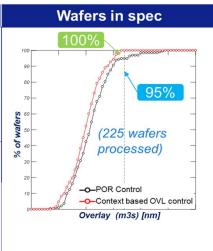

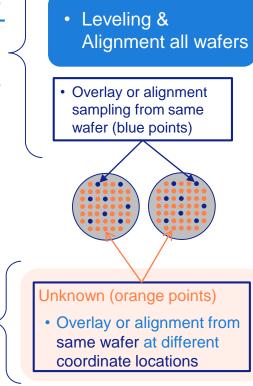

#### Context based Overlay Control results

Predict dense alignment from dense leveling data hybrid metrology enabled by machine learning Type 1

ASML

Public Slide 17

Known input

Prediction

Machine Learning

Pairing wafer leveling metrology from a lithographic apparatus with deep learning to enable cost effective dense wafer alignment metrology

E. Schmitt-Weaver & K. Bhattacharyya, SPIE 2019, 10961-7

## Holistic Lithography delivering significant customer value ASML

Lithography scanner with advanced control capability

Public Slide 18

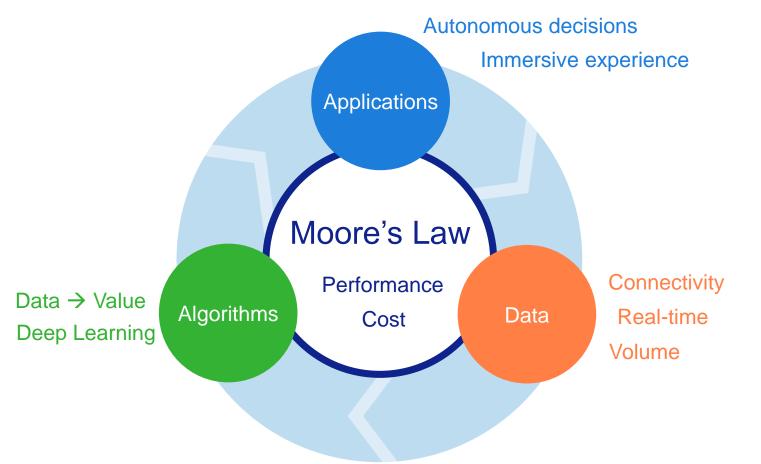

### Major trends in semiconductor-enabled computing

Public Slide 19

**ASML**