From lines and spaces to patterns and shapes

John Y. Chen

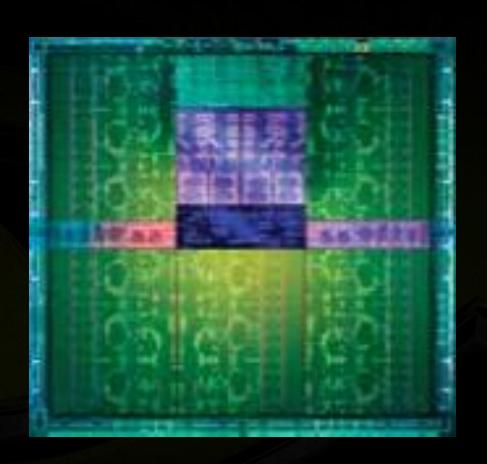

# Kepler GK110, a high performance chip for graphics and computing

•2048 SM cores made by 28nm Hk/MG tech

•7.1B X' tors

•19.7B contacts + 20.5B via's + 20Km 1x metal lines

•553 mm<sup>2</sup>

Jen-Hsun Huang's keynote at 2013 GPC

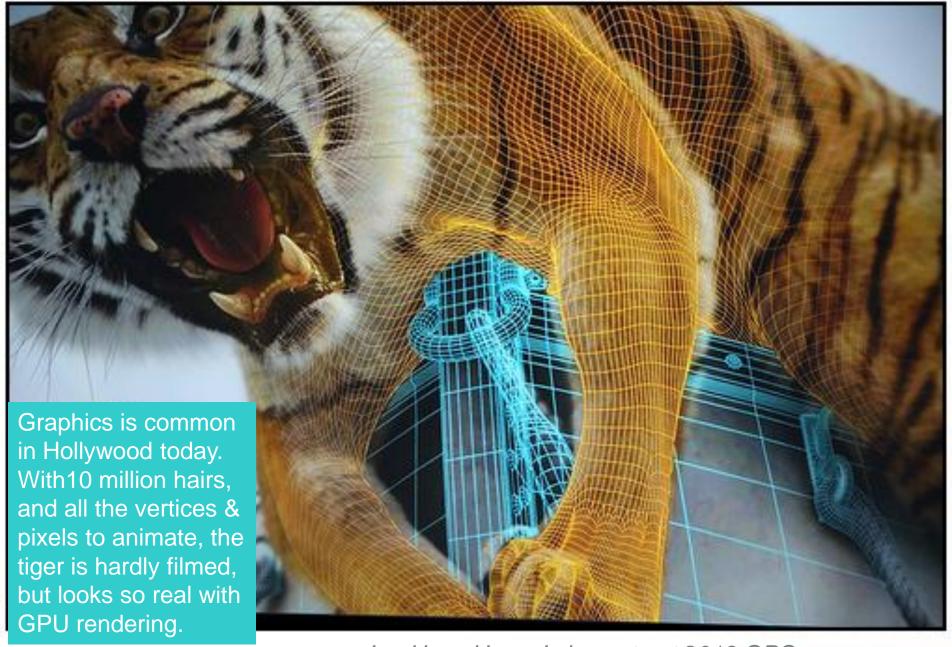

Showing off a digital tiger generated for 'Life of Pi' by Rhythm and Hues.

## Graphics vs. Mask making

| <u>Graphics</u>              | Mask making                |

|------------------------------|----------------------------|

| Vertices, Lines, & Triangles | Lines, spaces & rectangles |

| Geometries                   | Shapes                     |

| Pixel shading                | Dose and Contrast          |

| Photo realism                | Pattern replication        |

Both deal with images with huge data base

#### MOSIS CMOS SCALABLE RULES WELL POLY ( P WELL. N WELL ) -N36--d 6-1 P- REGION - 6 b SELECT CONTACT TO POLY CONTACT TO ACTIVE ( PSELECT-NSELECT ) BELECT POR CONTACTS EXACTLY 2x2 DENSER 1-2 SELECT FOR XTOR METAL1 LAYER COLOR WELL PWELL POLY OR ACTIVE VIA NWELL ACTIVE SELECT CSG PSELECT EXACTLY 2x2 NSELECT CSN POLY GLASS CONT TO POLY CCP METAL2 CONT TO ACT CCA METAL1 CMF 5 изсвоия VIA CVA METAL2 GLASS COG BONDING PRD 188×188 U METAL2 REQUIRED UNDER GLASS CUT ALL LAYERS EXCEPT METALS MUST BE ON A LAMBOR HETALS MUST BE ON A HALF LAMBOR DAID

## MOSIS offering in the 80's

Scalable Design Rules drawn by unit of  $\lambda$ , ( $\lambda$  scales w/ technology node)

All lines/spaces on one page

John Y. Chen, "CMOS Devices and Technology for VLSI," Prentice Hall, 1990.

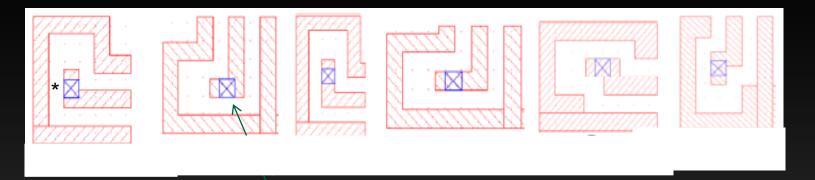

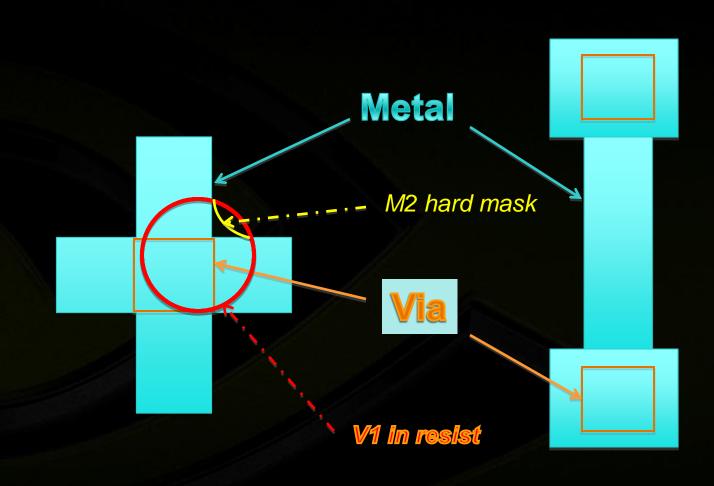

## L-shape metal pattern with via above

#### <u>Via Layout:</u>

- L shaped underlying metal line

- 0/min enclosure on x/y

- 4 corners with another surrounding metal -> OPC unfriendly

- DFM down to 1% for this type

- To guarantee the min space needed for TDDB Reliability, how tight the control needs to be ?

#### **Process control:**

- Precise Litho

- Etch with min μ-loading

- Perfect Cu fill

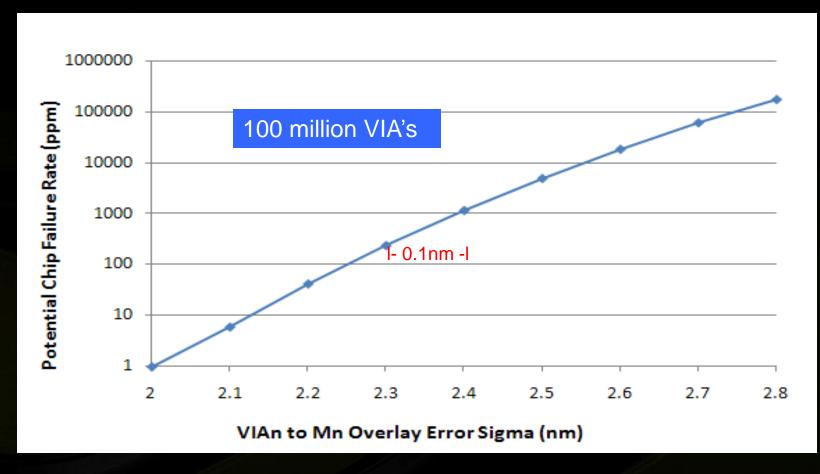

### Control down to 0.1nm, every tenth nm counts!

32nm drawn rule for min Mn and VIAn in a 20nm design

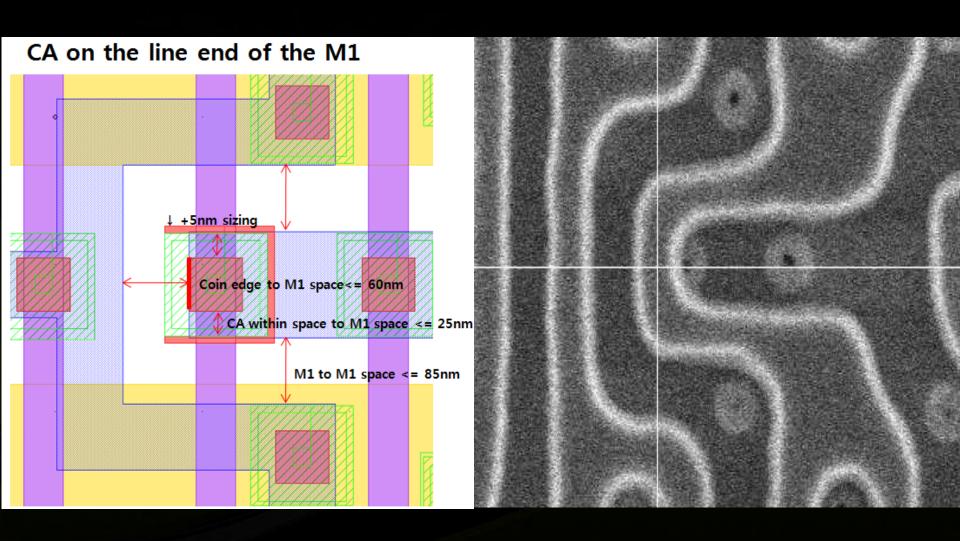

## **Crosses and Dogbones**

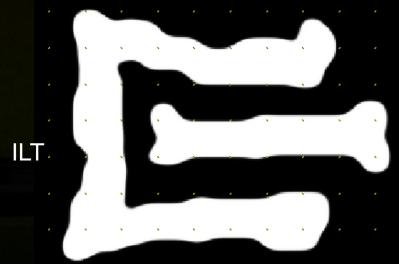

## E-shape metal over contact

## The E-shape metal

Margins gained by using ILT w/MB-MDP (Model Based Mask Data Preparation)

MB-MDP Shots

Mask

Precision

Thruput

**Si**Printable

Manufacturable

+ MDP

ILT

Min shots

(What's in Si vs. What's in Drawn)

+ OPC

Proximity

correction

\* **GDS**Small die

Min patterns restrictio

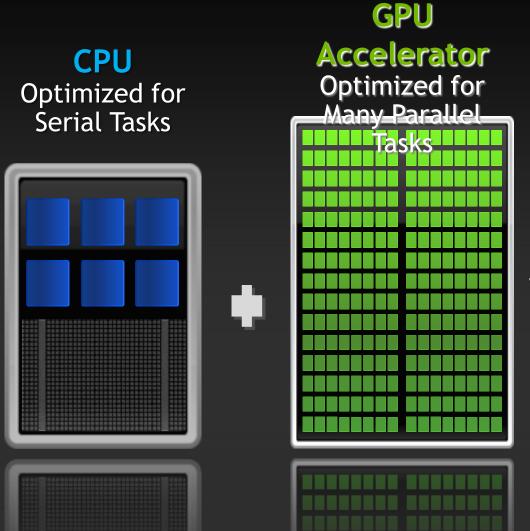

## **Accelerated Computing**

Multi-core plus Many-cores

10x Performance

5x Energy Efficiency